# T32CZ20

Sub-GHz Z-Wave RF SoC

### **Description**

The T32CZ20 is an ultra-low power, high performance Sub-GHz wireless SoC supporting Z-Wave to facilitate sensor network, building automation, smart locks and smart home applications.

Harnessing the power of ARM Cortex®-M33 and TrustZone technology, the T32CZ20 SoC establishes secure enclaves to safeguard critical data and processes. The integration of Physical Unclonable Function (PUF) adds an extra layer of security by leveraging unique physical variations within the chip to generate device-specific cryptographic keys, enhancing resistance to cloning. Complementing these features, the True Random Number Generator (TRNG) ensures the generation of unpredictable and truly random numbers, vital for cryptographic operations and secure communications.

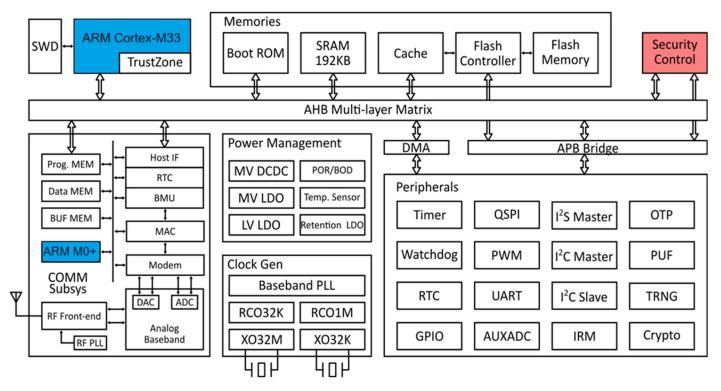

Figure 1 T32CZ20 Block Diagram

# **Table of Contents**

| De  | escription      |                                |    |  |  |

|-----|-----------------|--------------------------------|----|--|--|

| Tab | ole of Con      | ntents                         | 2  |  |  |

| 1.  | Introduc        | ction                          | 7  |  |  |

|     | 1.1.            | Features                       | 9  |  |  |

| 2.  | Host CF         | PU                             | 10 |  |  |

|     | 2.1.            | CPU Configuration Supported    | 10 |  |  |

|     | 2.2.            | Memory Map                     | 10 |  |  |

|     | 2.3.            | Memory Banks                   | 13 |  |  |

|     | 2.4.            | Interrupts                     | 13 |  |  |

| 3.  | Clocks.         |                                | 15 |  |  |

|     | 3.1.            | The 32 MHz Crystal Oscillator  | 15 |  |  |

|     | 3.2.            | The Baseband PLL               | 15 |  |  |

|     | 3.3.            | The 1 MHz RC Oscillator        | 16 |  |  |

|     | 3.4.            | The 32 KHz RC Oscillator       | 17 |  |  |

|     | 3.5.            | The 32 KHz Crystal Oscillator  | 17 |  |  |

|     | 3.6.            | Internal Clocks                | 18 |  |  |

|     | 3.7.            | Registers of Clock Control     | 22 |  |  |

| 4.  | Resets          |                                | 25 |  |  |

|     | 4.1.            | Power-on Reset                 | 26 |  |  |

|     | 4.2.            | External Reset                 | 26 |  |  |

|     | 4.3.            | Deep Power-down Wakeup Reset   | 26 |  |  |

|     | 4.4.            | Deepsleep Wakeup Reset         | 26 |  |  |

|     | 4.5.            | Watchdog Reset                 | 26 |  |  |

|     | 4.6.            | Software Reset                 | 26 |  |  |

|     | 4.7.            | MCU Lockup                     | 27 |  |  |

|     | 4.8.            | Registers of Reset Causes      | 27 |  |  |

| 5.  | Low Power Modes |                                | 28 |  |  |

|     | 5.1.            | Power Domains of Peripherals   | 29 |  |  |

|     | 5.2.            | Power Modes of COMM Subsys     | 30 |  |  |

|     | 5.3.            | Wakeup in Sleep Mode           | 30 |  |  |

|     | 5.4.            | Wakeup in Deep Sleep Mode      | 31 |  |  |

|     | 5.5.            | Wakeup in Deep Power-down Mode | 31 |  |  |

|     | 5.6.        | Memory Low-power Control          | 32 |

|-----|-------------|-----------------------------------|----|

|     | 5.7.        | Registers                         | 36 |

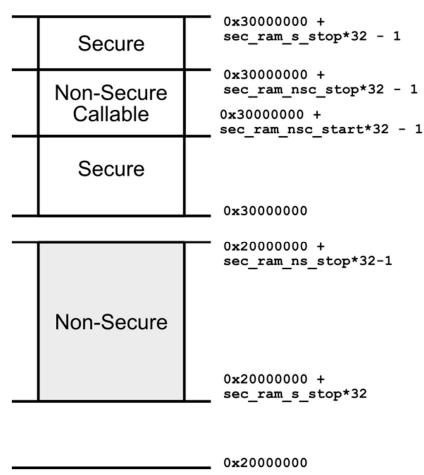

| 6.  | Security    | Controller                        | 41 |

|     | 6.1.        | Region ID                         | 41 |

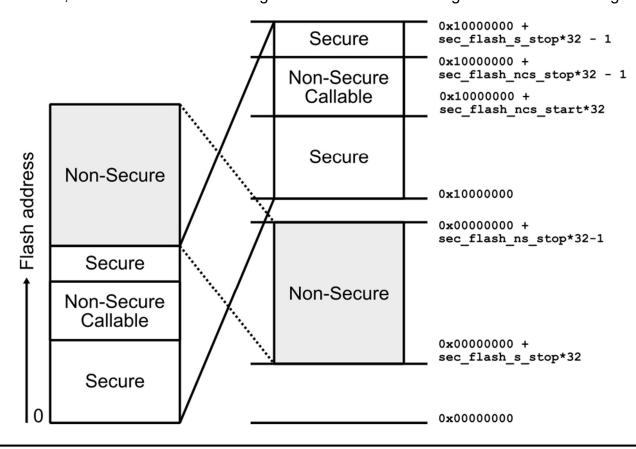

|     | 6.2.        | Security Partition of Flash       | 42 |

|     | 6.3.        | Security Partition of RAM         | 43 |

|     | 6.4.        | Security Partition of Peripherals | 44 |

|     | 6.5.        | Registers                         | 46 |

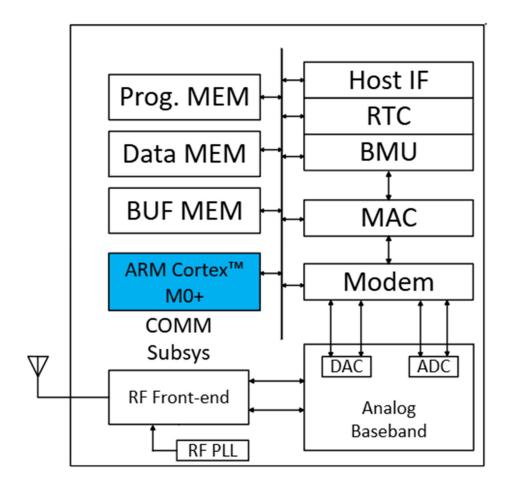

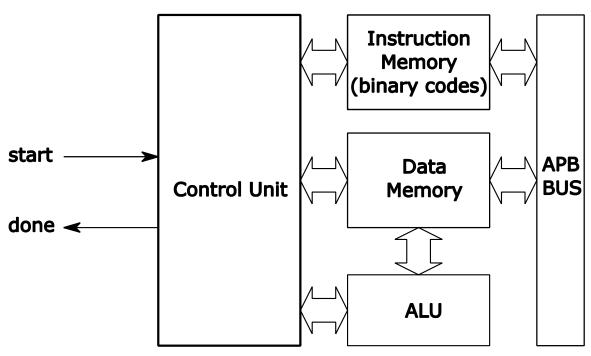

| 7.  | COMM Subsys |                                   |    |

|     | 7.1.        | Block Diagram                     | 51 |

|     | 7.2.        | Cortex M0+ MCU                    | 52 |

|     | 7.3.        | Buffer Memory                     | 52 |

|     | 7.4.        | Host Interface                    | 52 |

|     | 7.5.        | Host Mode and MCU Mode            | 54 |

|     | 7.6.        | Registers                         | 55 |

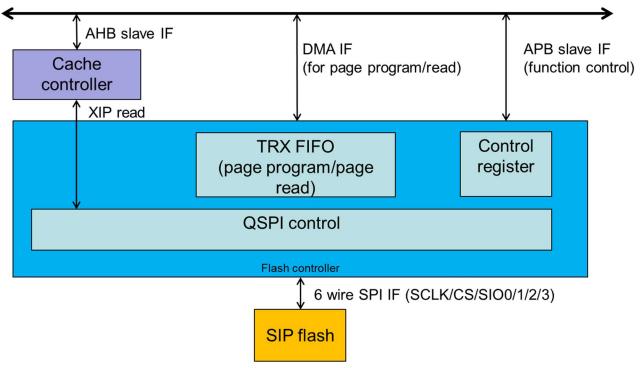

| 8.  | Flash Co    | ontrol                            | 58 |

|     | 8.1.        | Block Diagram                     | 58 |

|     | 8.2.        | Registers                         | 58 |

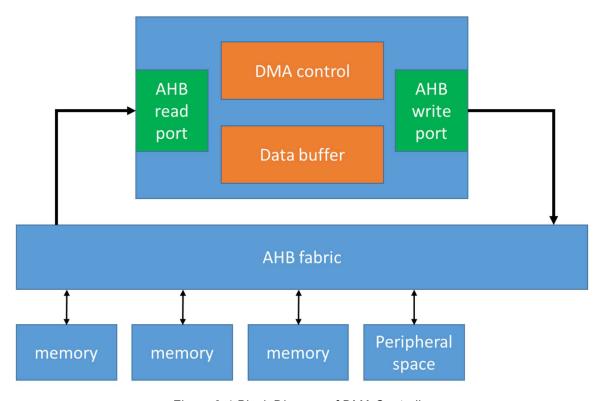

| 9.  | DMA         |                                   | 63 |

|     | 9.1.        | Block Diagram                     | 63 |

|     | 9.2.        | Features                          | 63 |

|     | 9.3.        | Functional Description            | 64 |

|     | 9.4.        | Registers                         | 64 |

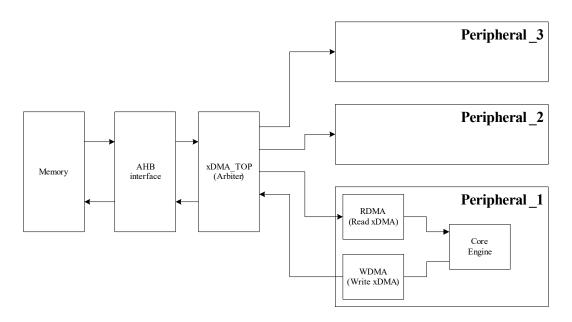

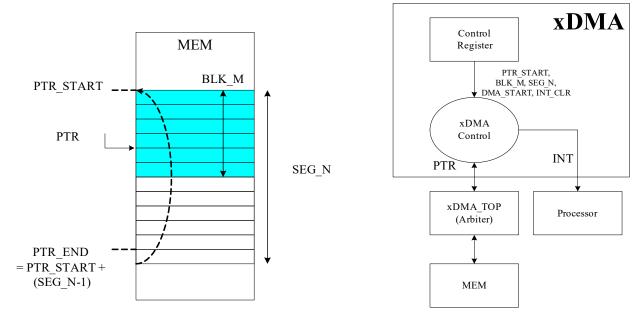

| 10. |             | xDMA                              | 66 |

|     | 10.1.       | Block Diagram                     | 66 |

|     | 10.2.       | Functional Descriptions           | 66 |

|     | 10.3.       | Registers                         | 69 |

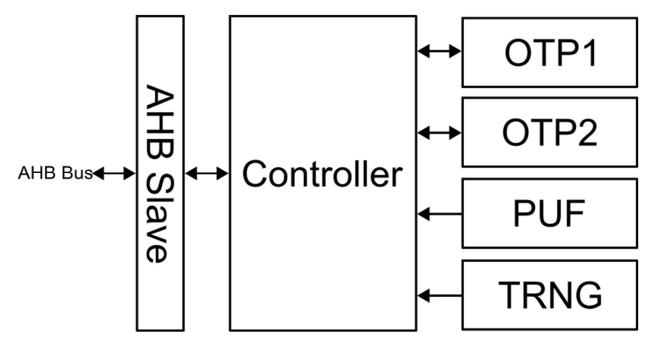

| 11. |             | PUFrt                             | 70 |

|     | 11.1.       | PUF                               | 70 |

|     | 11.2.       | OTP                               | 71 |

|     | 11.3.       | PUF and OTP Zeroization           | 72 |

|     | 11.4.       | TRNG                              | 72 |

|     | 11.5.       | Registers                         | 73 |

| 12. |             | Software IRQ                      | 75 |

|     | 12.1.       | Registers                         | 75 |

|     |             |                                   |    |

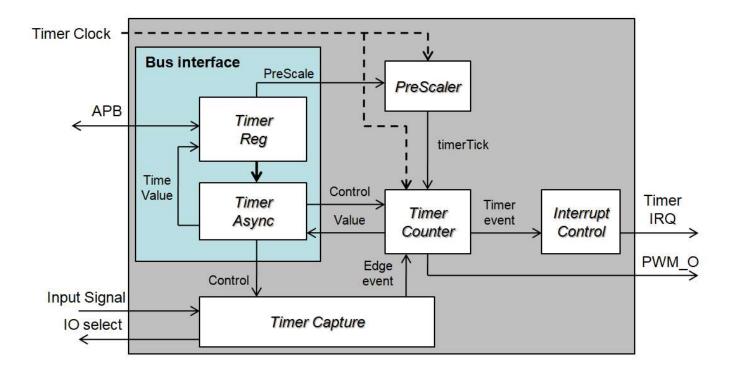

| 13.   | Timer                    | 76  |

|-------|--------------------------|-----|

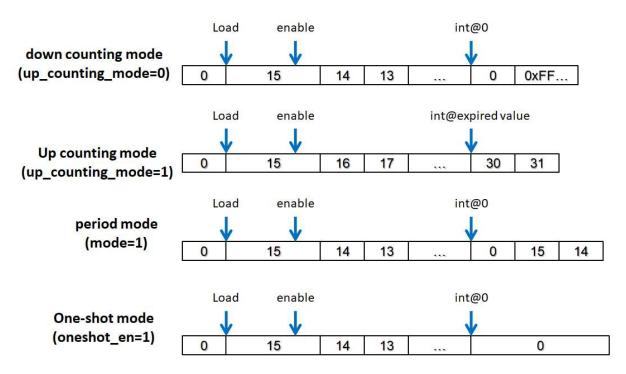

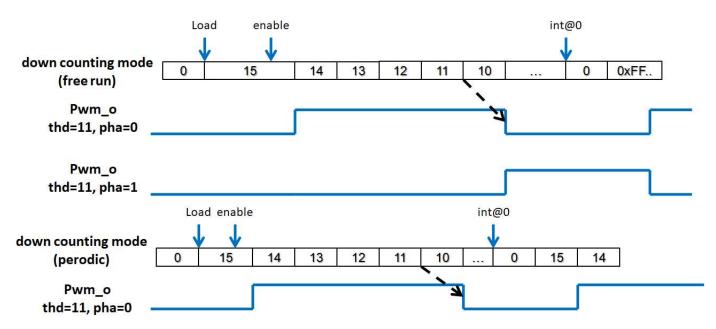

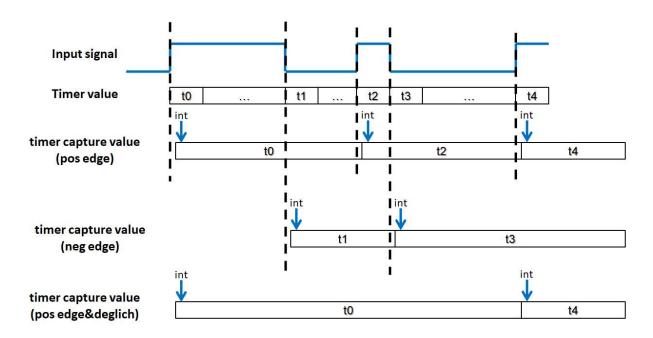

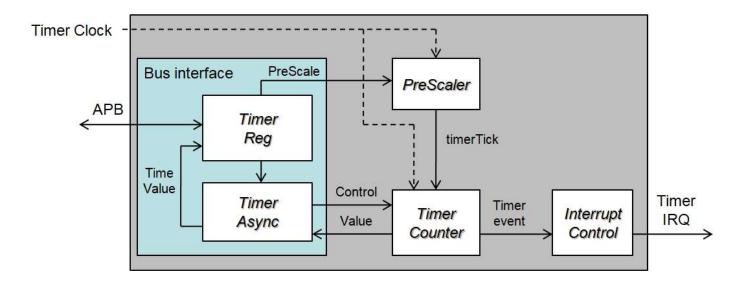

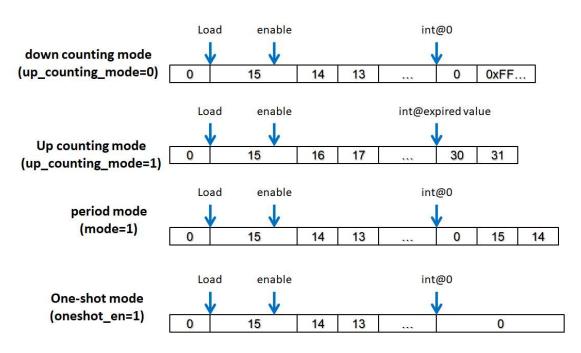

| 13.1. | Block Diagram            | 77  |

| 13.2. | Functional Description   | 77  |

| 13.3. | Registers                | 81  |

| 14.   | Slow-clock Timer         | 84  |

| 14.1. | Block Diagram            | 84  |

| 14.2. | Functional Descriptions  | 84  |

| 14.3. | Registers                | 86  |

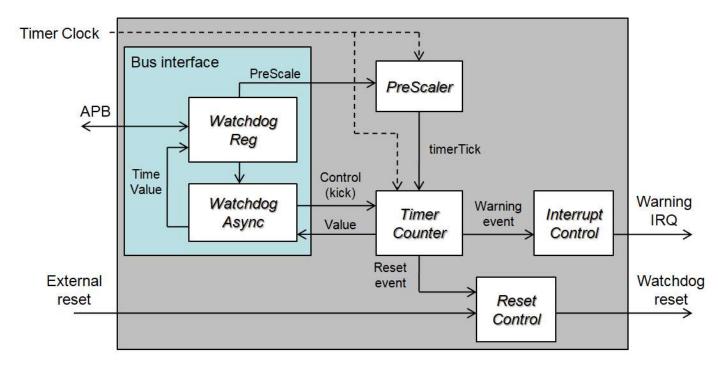

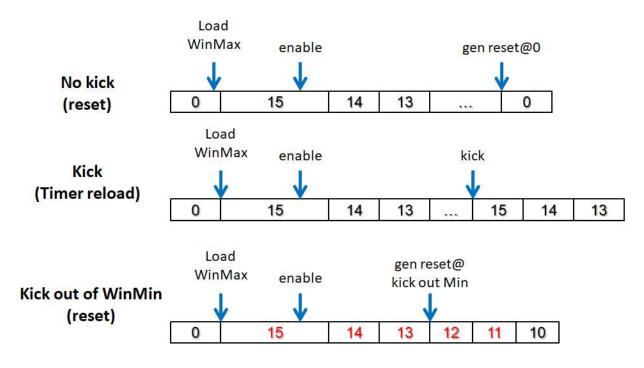

| 15.   | Watchdog Timer           | 88  |

| 15.1. | Block Diagram            | 88  |

| 15.2. | Functional Descriptions  | 89  |

| 15.3. | Registers                | 90  |

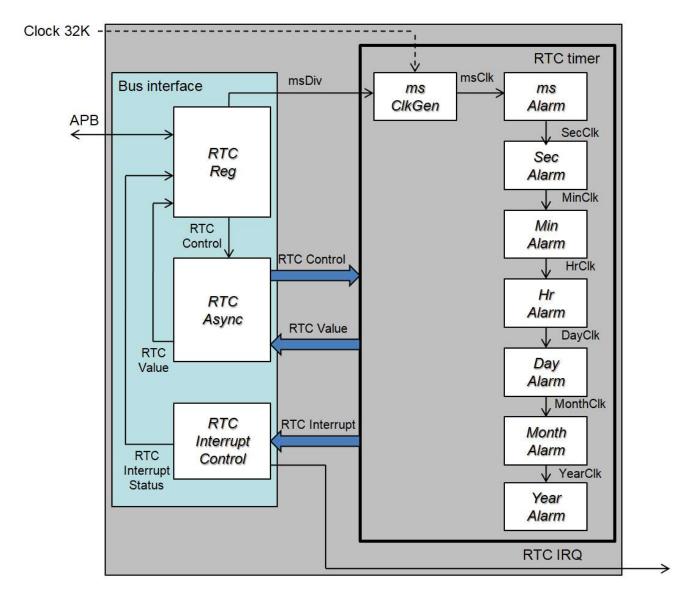

| 16.   | RTC Timer                | 93  |

| 16.1. | Block Diagram            | 94  |

| 16.2. | Function Description     | 94  |

| 16.3. | Registers                | 98  |

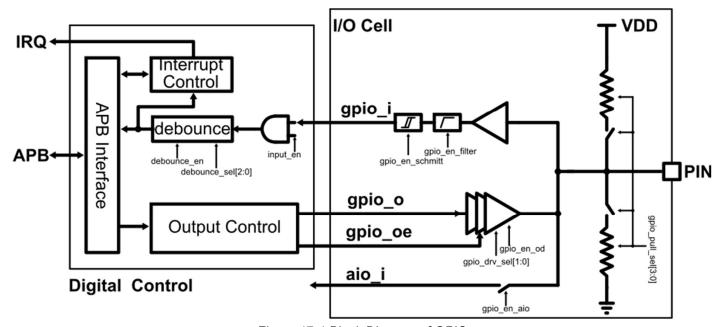

| 17.   | GPIO Control             | 103 |

| 17.1. | Block Diagram            | 103 |

| 17.2. | Functional Description   | 103 |

| 17.3. | GPIO Multi-function MUXs | 105 |

| 17.4. | Registers                | 106 |

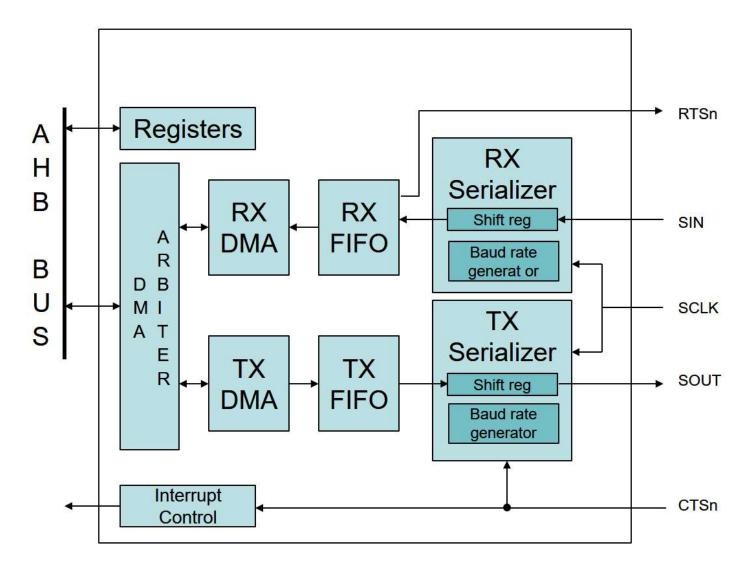

| 18.   | UART                     | 126 |

| 18.1. | Block Diagram            | 126 |

| 18.2. | Features                 | 127 |

| 18.3. | Functional Description   | 127 |

| 18.4. | Registers                | 134 |

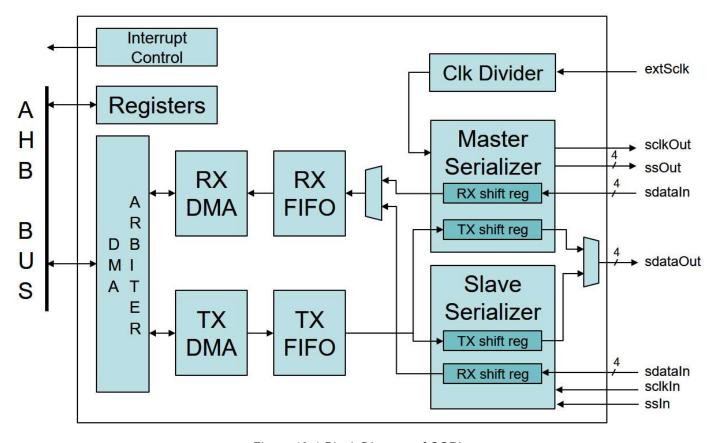

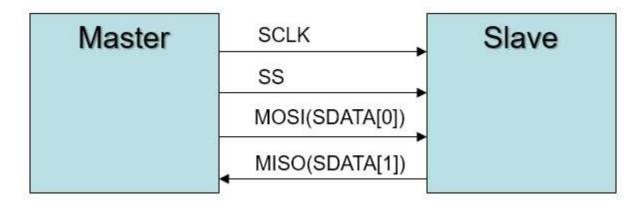

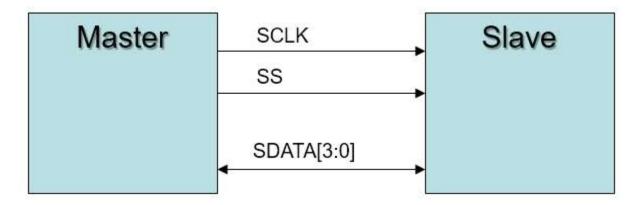

| 19.   | QSPI                     | 138 |

| 19.1. | Block Diagram            | 138 |

| 19.2. | Features                 | 138 |

| 19.3. | Functional Description   | 139 |

| 19.4. | Registers                | 141 |

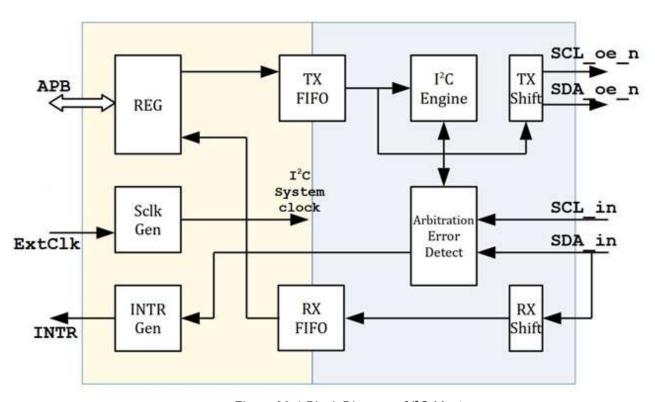

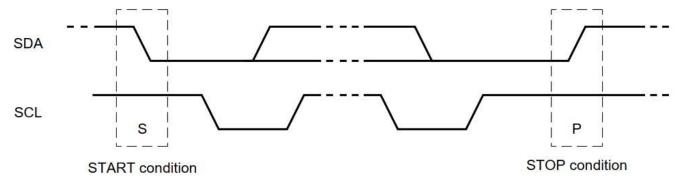

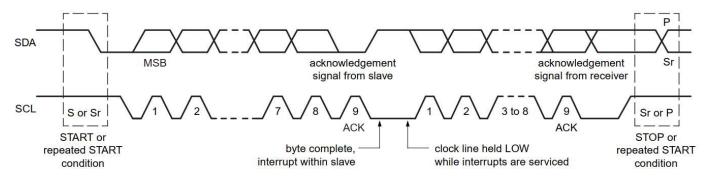

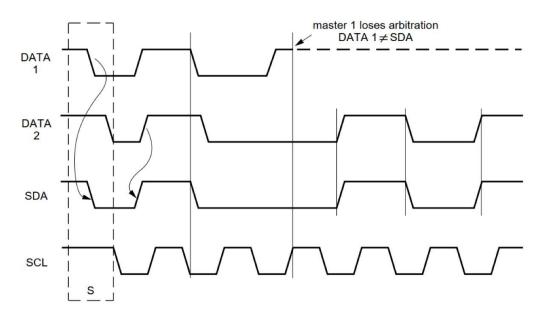

| 20.   | I <sup>2</sup> C Master  | 149 |

| 20.1. | Block Diagram            | 149 |

| 20.2. | Functional Descriptions  | 150 |

| 20.3. | Programming Sequences    | 153 |

|       |                          |     |

|     | 20.4. | Registers               | 154 |

|-----|-------|-------------------------|-----|

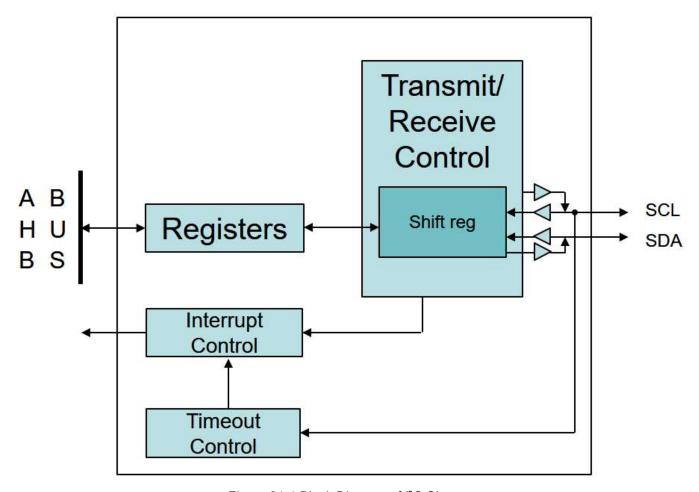

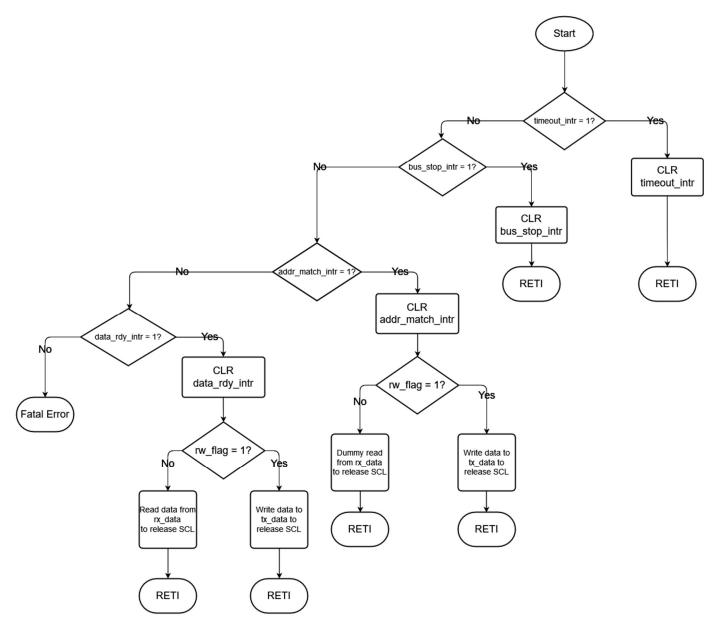

| 21. |       | I <sup>2</sup> C Slave  | 158 |

|     | 21.1. | Block Diagram           | 159 |

|     | 21.2. | Functional Description  | 159 |

|     | 21.3. | Registers               | 161 |

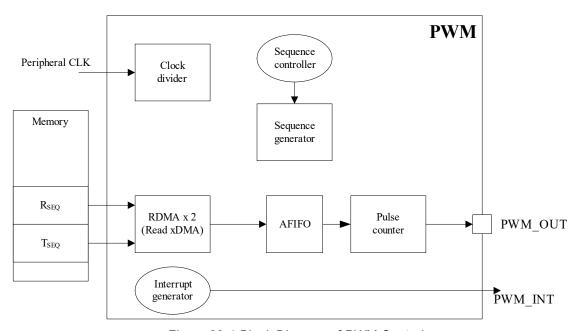

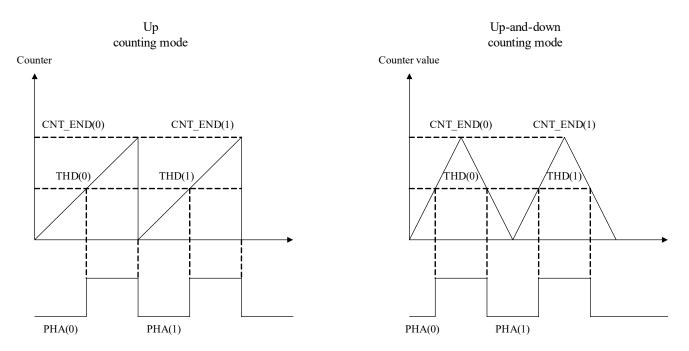

| 22. |       | PWM                     | 164 |

|     | 22.1. | Block Diagram           | 164 |

|     | 22.2. | Features                | 164 |

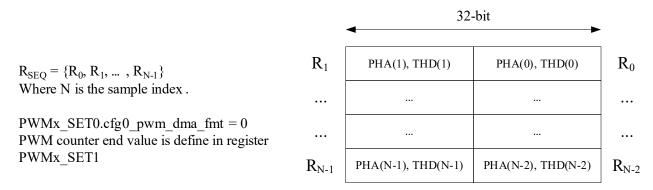

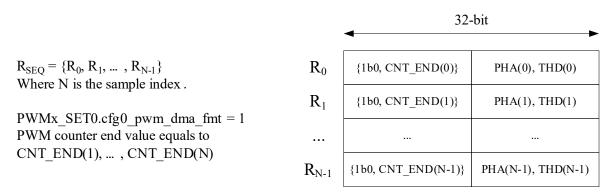

|     | 22.3. | Functional Description  | 165 |

|     | 22.4. | Registers               | 169 |

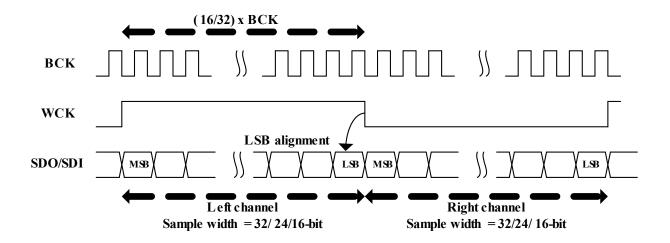

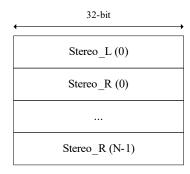

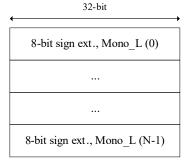

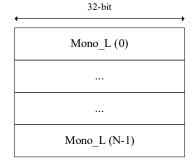

| 23. |       | I <sup>2</sup> S        | 176 |

|     | 23.1. | Block Diagram           | 176 |

|     | 23.2. | Features                | 176 |

|     | 23.3. | Sample Rate Settings    | 177 |

|     | 23.4. | Interface Modes         | 178 |

|     | 23.5. | xDMA Supports           | 179 |

|     | 23.6. | Registers               | 180 |

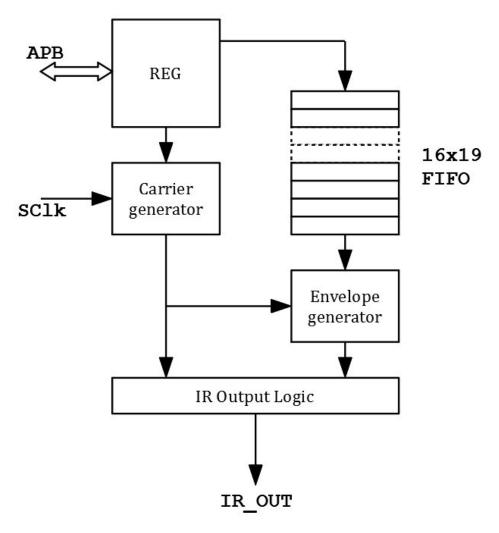

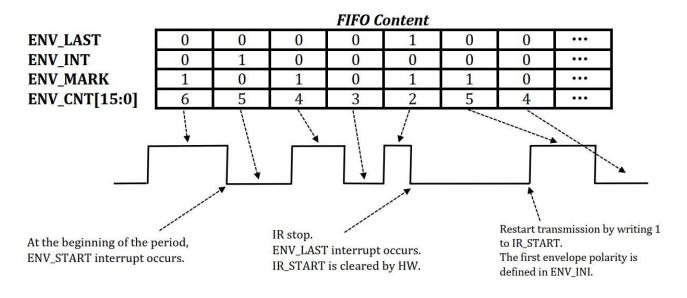

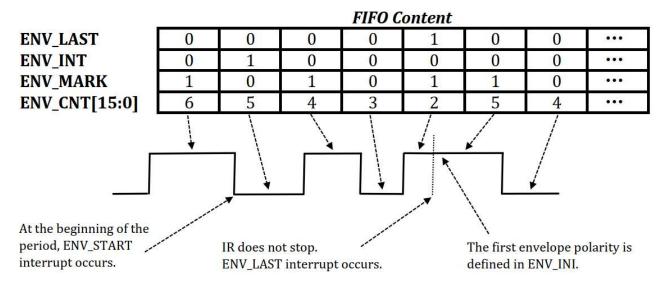

| 24. |       | IRM                     | 187 |

|     | 24.1. | Block Diagram           | 187 |

|     | 24.2. | Features                | 188 |

|     | 24.3. | Functional Description  | 188 |

|     | 24.4. | Registers               | 191 |

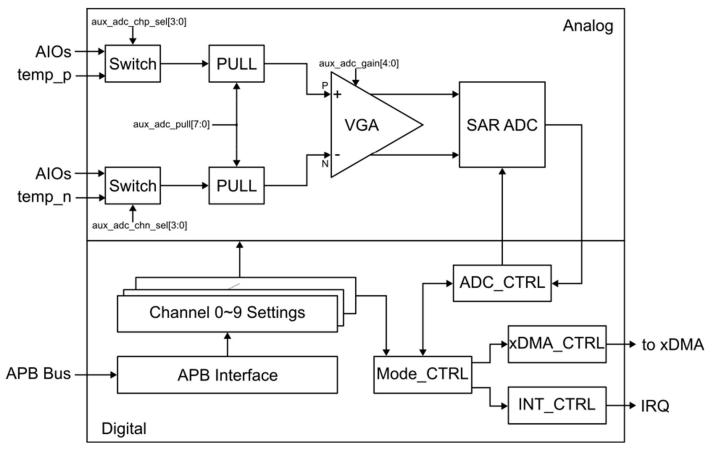

| 25. |       | AUX ADC                 | 195 |

|     | 25.1. | Block Diagram           | 195 |

|     | 25.2. | Features                | 196 |

|     | 25.3. | Functional Description  | 196 |

|     | 25.4. | Registers               | 200 |

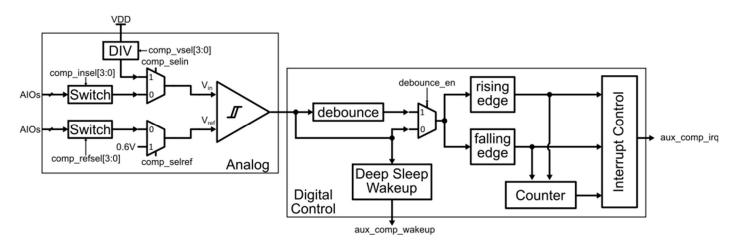

| 26. |       | AUX Comparator          | 207 |

|     | 26.1. | Block Diagram           | 207 |

|     | 26.2. | Functional Descriptions | 207 |

|     | 26.3. | Registers               | 208 |

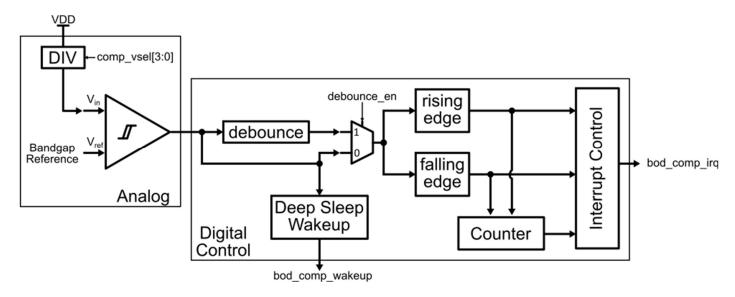

| 27. |       | BOD Comparator          | 211 |

|     | 27.1. | Registers               | 211 |

| 28. |       | Crypto Engine           | 214 |

|     | 28.1. | Block Diagram           | 214 |

|     |       |                         |     |

|     | 28.2. | Features                          | 214 |

|-----|-------|-----------------------------------|-----|

|     | 28.3. | Functional Description            | 215 |

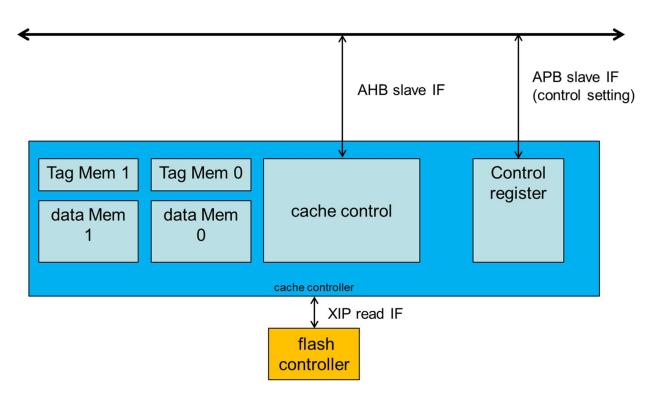

| 29. |       | Cache Controller                  | 216 |

|     | 29.1. | Registers                         | 217 |

| 30. |       | Reference Manual Revision History | 218 |

| 31. |       | Contact Us                        | 219 |

|     | 31.1. | Support                           | 219 |

### 1. Introduction

The T32CZ20 is an ultra-low power, high performance Sub-GHz wireless SoC for the Z-Wave Long Range wireless communication protocol network for automation, smart locks and smart home, and security applications. It features an integrated ARM Cortex®-M33 core with a rich set of peripherals and an integrated wireless transceiver with its own dedicated ARM Cortex®-M0+ core. It is efficient enough for low-power end-devices and powerful enough for integrating Z-Wave Controllers into base stations, hubs, bridges, security panels etc. This makes the T32CZ20 ideal for battery-powered devices and applications where both performance and energy efficiency are essential.

The Z-Wave Long Range communication protocol propagates better through walls and has much less interference than the crowded 2.4GHz band using spread spectrum technology to transmit at much higher power and still be well within RF regulatory limits dynamically adapting RF power when needed to conserve power and has much better latency and overall downstream performance and capabilities than LoRa.

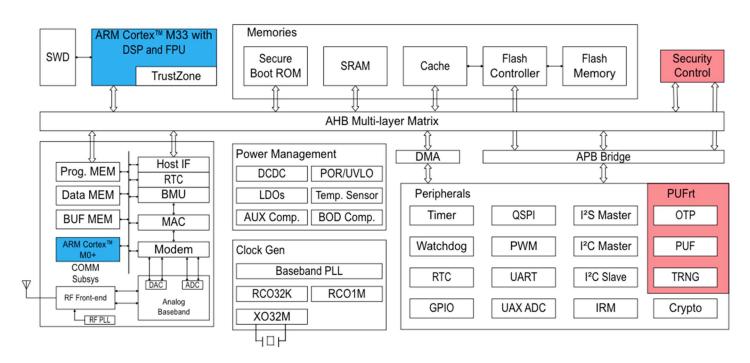

Figure 1-1 CZ20 Block Diagram

There are two subsystems inside the CZ20 with 288KB total SRAM:

- host subsystem with high to 64 MHz 32-bit ARM Cortex-M33, 192KB SRAM and up to 2MB Flash for application requirements

- communication subsystem (COMM Subsys) with ARM Cortex-M0+ MCU and a HW MAC accelerator utilizing 96KB program SRAM for dynamic switching between standard protocols to support multiple simultaneous unique links.

Through the whole document, Host CPU indicates Cortex-M33 and MCU indicates Cortex-M0+.

#### 1.1. Features

- Host CPU

- ARM Cortex-M33

- 32 KB Boot ROM with Secure Boot function

- 192 KB SRAM

- Clock frequencies support up to 64

MHz

- XIP (eXecute In Place) Flash with Cache

- Peripherals

- DMA x2

- General Timer x3

- Slow clock Timer x2

- Watchdog Timer

- RTC Timer

- GPIO up to 22

- (Q)SPI x2

- PWM x5

- UART x3

- I<sup>2</sup>S Master

- I<sup>2</sup>C Master x2

- I<sup>2</sup>C Slave

- IRM (Infrared Modulator)

- BOD Comparator

- AUX Comparator

- AUX ADC up to 4 channels

- Security Peripherals

- Secure OTP

- PUF (Physical Unclonable Function)

- TRNG

- Cryptographic accelerator

- ◆ AES

- ◆ SHA256

- ◆ ECC/ECDSA/ECDH

- Clocks

- Baseband PLL up to 72MHz

- 32 MHz crystal oscillator

- 1 MHz RC oscillator

- 32 KHz RC oscillator

- 32 KHz crystal oscillator (supported only in certain packages)

- Low-power modes

- CPU Wait-for-interrupt (WFI)

- Sleep mode

- Deep sleep mode

- Deep power-down mode

- Power Managements

- POR

- BOD

- Buck DCDC

- LDOs

- COMM Subsys

- ARM Cortex-M0+

- 96 KB SRAM for program memory (can be shared with Cortex-M33)

- 8 KB SRAM for data memory

- 8 KB SRAM for TX/RX data buffers

- Multi-protocol Modem and Link control

- Independent AES/CCM engine for onthe-fly encryption/decryption

### 2. Host CPU

The Cortex-M33 CPU is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- outstanding processing performance combined with fast interrupt handling

- efficient processor core, system and memories

- ultra-low power consumption with integrated sleep modes

- platform security robustness with TrustZone

# 2.1. CPU Configuration Supported

Table 2-1 Configurable options of Cortex-M33 in CZ20

|            | Description                        | Implementation                                  |

|------------|------------------------------------|-------------------------------------------------|

| FPU        | Floating Point Unit                | YES                                             |

| DSP        | DSP Extension                      | YES                                             |

| SECEXT     | Security Extension                 | YES                                             |

| SAU        | Security Attribution Unit          | YES (Use platform-defined security control unit |

|            |                                    | instead)                                        |

| NUMIRQ     | Number of IRQ inputs               | 48                                              |

| IRQLVL     | Control bits of IRQ priority level | 3 (8 levels)                                    |

| DBGLVL     | Debug level                        | 2 (Full set of debug resources)                 |

| ITM        | Instrumentation Trace Macrocell    | No                                              |

| ETM        | Embedded Trace Macrocell           | No                                              |

| MTB        | Micro Trace Buffer                 | No                                              |

| WIC        | Wake-up Interrupt Controller       | Yes                                             |

| Endianness | Memory system endianness           | Little endian                                   |

| JTAG/SWD   | Debug Interface                    | SWD only                                        |

# 2.2. Memory Map

Table 2-2 Memory Map

| Modules  | Size  | Non-secure Address     | Secure Address        |

|----------|-------|------------------------|-----------------------|

| Flash    | 128MB | 0x000000000~0x07FFFFFF | 0x10000000~0x17FFFFF  |

| Boot ROM | 32KB  | N/A                    | 0x18000000~0x18007FFF |

| Modules  | Size  | Non-secure Address     | Secure Address        |

| Bassassa                |      |                       |                       |

|-------------------------|------|-----------------------|-----------------------|

| Reserved                |      | 0x08008000~0x0FFFFFF  | 0x18008000~0x1FFFFFF  |

| RAM 0                   | 32KB | 0x20000000~0x20007FFF | 0x30000000~0x30007FFF |

| RAM 1                   | 32KB | 0x20008000~0x2000FFFF | 0x30008000~0x3000FFFF |

| RAM 2                   | 32KB | 0x20010000~0x20017FFF | 0x30010000~0x30017FFF |

| RAM 3                   | 32KB | 0x20018000~0x2001FFFF | 0x30018000~0x3001FFFF |

| RAM 4                   | 32KB | 0x20020000~0x20027FFF | 0x30020000~0x30027FFF |

| RAM 5                   | 16KB | 0x20028000~0x2002BFFF | 0x30028000~0x3002BFFF |

| RAM 6                   | 16KB | 0x2002C000~0x2002FFFF | 0x3002C000~0x3002FFFF |

| Reserved                |      | 0x20030000~0x2003FFFF | 0x30030000~0x3003FFFF |

| COMM Subsys RAM         | 96KB | 0x20040000~0x20057FFF | 0x30040000~0x30057FFF |

| Reserved                |      | 0x20030000~0x2FFFFFF  | 0x30030000~0x3FFFFFF  |

| System Control          | 4KB  | 0x40000000~0x40000FFF | 0x50000000~0x50000FFF |

| GPIO Control            | 4KB  | 0x40001000~0x40001FFF | 0x50001000~0x50001FFF |

| Reserved                |      | 0x40002000~0x40002FFF | 0x50002000~0x50002FFF |

| Security Control        | 4KB  | N/A                   | 0x50003000~0x50003FFF |

| RTC Timer               | 4KB  | 0x40004000~0x40004FFF | 0x50004000~0x50004FFF |

| Deep Power-down Control | 4KB  | 0x40005000~0x40005FFF | 0x50005000~0x50005FFF |

| Power Management        | 4KB  | 0x40006000~0x40006FFF | 0x50006000~0x50006FFF |

| Reserved                |      | 0x40007000~0x40007FFF | 0x50007000~0x50007FFF |

| Reserved                |      | 0x40008000~0x40008FFF | 0x50008000~0x50008FFF |

| Flash Control           | 4KB  | 0x40009000~0x40009FFF | 0x50009000~0x50009FFF |

| Timer 0                 | 4KB  | 0x4000A000~0x4000AFFF | 0x5000A000~0x5000AFFF |

| Timer 1                 | 4KB  | 0x4000B000~0x4000BFFF | 0x5000B000~0x5000BFFF |

| Timer 2                 | 4KB  | 0x4000C000~0x4000CFFF | 0x5000C000~0x5000CFFF |

| Slow-clock Timer 0      | 4KB  | 0x4000D000~0x4000DFFF | 0x5000D000~0x5000DFFF |

| Slow-clock Timer 1      | 4KB  | 0x4000E000~0x4000EFFF | 0x5000E000~0x5000EFFF |

| Reserved                |      | 0x4000F000~0x4000FFFF | 0x5000F000~0x5000FFFF |

| Watchdog Timer          | 4KB  | 0x40010000~0x40010FFF | 0x50010000~0x50010FFF |

| Reserved                |      | 0x40011000~0x40011FFF | 0x50011000~0x50011FFF |

| UART 0                  | 4KB  | 0x40012000~0x40012FFF | 0x50012000~0x50012FFF |

| UART 1                  | 4KB  | 0x40013000~0x40013FFF | 0x50013000~0x50013FFF |

| Reserved                |      | 0x40014000~0x40014FFF | 0x50014000~0x50014FFF |

| Reserved                |      | 0x40015000~0x40015FFF | 0x50015000~0x50015FFF |

| Modules                 | Size | Non-secure Address    | Secure Address        |

| Reserved                |      | 0x40016000~0x40016FFF | 0x50016000~0x50016FFF |

| Reserved                |      | 0x40017000~0x40017FFF | 0x50017000~0x50017FFF |

|                         |      |                       | •                     |

| I <sup>2</sup> C Slave    | 4KB  | 0x40018000~0x40018FFF | 0x50018000~0x50018FFF |

|---------------------------|------|-----------------------|-----------------------|

| Reserved                  |      | 0x40019000~0x40019FFF | 0x50019000~0x50019FFF |

| COMM Subsys               | 4KB  | 0x4001A000~0x4001AFFF | 0x5001A000~0x5001AFFF |

| Reserved                  |      | 0x4001B000~0x4001BFFF | 0x5001B000~0x5001BFFF |

| Reserved                  |      | 0x4001C000~0x4001CFFF | 0x5001C000~0x5001CFFF |

| BOD Comparator            | 4KB  | 0x4001D000~0x4001DFFF | 0x5001D000~0x5001DFFF |

| AUX Comparator            | 4KB  | 0x4001E000~0x4001EFFF | 0x5001E000~0x5001EFFF |

| Reserved                  |      | 0x4001F000~0x4001FFFF | 0x5001F000~0x5001FFFF |

| QSPI 0                    | 4KB  | 0x40020000~0x40020FFF | 0x50020000~0x50020FFF |

| QSPI 1                    | 4KB  | 0x40021000~0x40021FFF | 0x50021000~0x50021FFF |

| Reserved                  |      | 0x40022000~0x40022FFF | 0x50022000~0x50022FFF |

| Reserved                  |      | 0x40023000~0x40023FFF | 0x50023000~0x50023FFF |

| IRM                       | 4KB  | 0x40024000~0x40024FFF | 0x50024000~0x50024FFF |

| UART 2                    | 4KB  | 0x40025000~0x40025FFF | 0x50025000~0x50025FFF |

| PWM                       | 4KB  | 0x40026000~0x40026FFF | 0x50026000~0x50026FFF |

| Reserved                  |      | 0x40027000~0x40027FFF | 0x50027000~0x50027FFF |

| xDMA                      | 4KB  | 0x40028000~0x40028FFF | 0x50028000~0x50028FFF |

| DMA 0                     | 4KB  | 0x40029000~0x40029FFF | 0x50029000~0x50029FFF |

| DMA 1                     | 4KB  | 0x4002A000~0x4002AFFF | 0x5002A000~0x5002AFFF |

| I <sup>2</sup> C Master 0 | 4KB  | 0x4002B000~0x4002BFFF | 0x5002B000~0x5002BFFF |

| I <sup>2</sup> C Master 1 | 4KB  | 0x4002C000~0x4002CFFF | 0x5002C000~0x5002CFFF |

| I <sup>2</sup> S          | 4KB  | 0x4002D000~0x4002DFFF | 0x5002D000~0x5002DFFF |

| Reserved                  |      | 0x4002E000~0x4002EFFF | 0x5002E000~0x5002EFFF |

| AUX ADC                   | 4KB  | 0x4002F000~0x4002FFFF | 0x5002F000~0x5002FFFF |

| Software IRQ 0            | 4KB  | 0x40030000~0x40030FFF | 0x50030000~0x50030FFF |

| Software IRQ 1            | 4KB  | 0x40031000~0x40031FFF | 0x50031000~0x50031FFF |

| Reserved                  |      | 0x40032000~0x4043FFFF | 0x50032000~0x5043FFFF |

| PUFrt                     | 32KB | 0x40044000~0x40047FFF | 0x50044000~0x50047FFF |

| Crypto Engine             | 16KB | 0x60000000~0x60003FFF | 0x70000000~0x70003FFF |

|                           |      |                       |                       |

# 2.3. Memory Banks

Memories are divided into four banks that are listed in Table 2-3. Memory accesses in different banks can be occurred concurrently. This can significantly boost the performance of the memory system.

Table 2-3 Memory Banks

| Banks | Size          | Memory |

|-------|---------------|--------|

| 0     | 64KD          | RAM 0  |

| 0     | 64KB          | RAM 1  |

| 4     | <b>1</b> 64KB | RAM 2  |

| I     |               | RAM 3  |

| 2     | 32KB          | RAM 4  |

| 2     | <b>3</b> 32KB | RAM 5  |

| 3     |               | RAM 6  |

# 2.4. Interrupts

Table 2-4 Interrupt Table

| IRQ Index | Source                    | Active State |

|-----------|---------------------------|--------------|

| 0         | GPIO                      | programmable |

| 1         | Timer 0                   | level high   |

| 2         | Timer 1                   | level high   |

| 3         | Timer 2                   | level high   |

| 4         | Slow-clock Timer 0        | level high   |

| 5         | Slow-clock Timer 1        | level high   |

| 6         | Watchdog Timer            | level high   |

| 7         | RTC Timer                 | level high   |

| 8         | N/A                       |              |

| 9         | Software IRQ 0            | level high   |

| 10        | Software IRQ 1            | level high   |

| 11        | N/A                       |              |

| 12        | DMA 0                     | level high   |

| 13        | DMA 1                     | level high   |

| 14        | N/A                       |              |

| 15        | N/A                       |              |

| 16        | UART 0                    | level high   |

| 17        | UART 1                    | level high   |

| 18        | UART 2                    | level high   |

| 19        | N/A                       |              |

| 20        | IRM                       | level high   |

| 21        | I <sup>2</sup> C Master 0 | level high   |

| 22        | I <sup>2</sup> C Master 1 | level high   |

| 23        | I <sup>2</sup> C Slave    | level high   |

|    | T                |              |

|----|------------------|--------------|

| 24 | N/A              |              |

| 25 | QSPI 0           | level high   |

| 26 | QSPI 1           | level high   |

| 27 | N/A              |              |

| 28 | N/A              |              |

| 29 | l <sup>2</sup> S | level high   |

| 30 | N/A              |              |

| 31 | N/A              |              |

| 32 | PWM 0            | level high   |

| 33 | PWM 1            | level high   |

| 34 | PWM 2            | level high   |

| 35 | PWM 3            | level high   |

| 36 | PWM 4            | level high   |

| 37 | N/A              |              |

| 38 | N/A              |              |

| 39 | Flash Control    | level high   |

| 40 | PUFrt            | level high   |

| 41 | Crypto Engine    | level high   |

| 42 | BOD Comparator   | programmable |

| 43 | N/A              |              |

| 44 | Security Control | level high   |

| 45 | COMM Subsys      | level high   |

| 46 | AUX ADC          | level high   |

| 47 | AUX Comparator   | programmable |

### 3. Clocks

There are several clock sources in CZ20 and they are summarized in Table 3-1.

**Clock Name** Type Typical Frequency Comment Crystal oscillator xtal\_clk 32 MHz The default clock for Host CPU, memories and peripherals. pll\_clk PLL 36/40/48/64 MHz A higher frequency clock for Host CPU and memories. RC oscillator rco1m 921.6 KHz An optional clock for UARTs operating in Sleep mode. rco32k RC oscillator 32 KHz The default clock for slow-clock timers. xo32k 32.768 KHz A high accuracy clock for replacing Crystal oscillator rco32k.

Table 3-1 Clock Sources of CZ20

## 3.1. The 32 MHz Crystal Oscillator

Since CZ20 is a SoC chip for wireless communications, a crystal oscillator of 32 MHz (xtal\_clk) is required for establishing communication links correctly. It is also the default clock for Host CPU, memories and peripherals after power on.

During low-power modes (refer to Chapter 5 Low Power Modes for details), the xtal\_clk is turned off to reduce the current consumption. After waking up from low-power modes, it will be turned on again. Those on/off procedures are controlled by Hardware automatically and is transparent to Software.

### 3.2. The Baseband PLL

The Baseband PLL (pll\_clk) provides a higher clock frequency than 32MHz that can boost the performance of Host CPU and memories. Available clock options of the Baseband PLL are 36, 40, 48, 64, and 72 MHz.

Like the xtal\_clk, if pll\_clk is enabled, it will be turned off in low-power modes and turned on after waking up from low-power modes automatically by Hardware.

It is very important to follow below procedures to enable the Baseband PLL or to change its frequency, otherwise the unstable clock may result in malfunction.

- Switch the CPU clock to xtal clk

- Disable Baseband PLL

- Set new frequency of Baseband PLL

- Enable Baseband PLL

- Wait 100u

- Switch the CPU clock to pll\_clk

The frequency of pll\_clk is selected by the register, cfg\_bbpll\_freq, which is summarized in Table 3-2.

| cfg_bbpll_freq[2:0] | Baseband PLL Frequency (MHz) |

|---------------------|------------------------------|

| 000b                | 48                           |

| 001b                | 64                           |

| 010b                | Reserved                     |

| 011b                | Reserved                     |

| 100b                | Reserved                     |

| 101b                | Reserved                     |

| 110b                | 36                           |

| 111b                | 40                           |

Table 3-2 Frequency Selections of Baseband PLL

### 3.3. The 1 MHz RC Oscillator

This 1 MHz RC Oscillator (rco1m) is primarily used for UARTs that are required to operate normally in low-power modes.

By default, all UARTs are clocked by the xtal\_clk after power-on. Since the xtal\_clk is turned off in low-power modes, the UART interface can't receive any data in low-power modes. This may not be a problem because for most applications CZ20 can decide when to communicate through the UART interface.

For applications that require UART communications at any time, we can let CZ20 not enter low-power modes with the cost of higher power consumptions. Alternatively, we can change the UART clock to rco1m so that the UART interface can still receive data in low-power modes. For this situation, we must first calibrate the frequency of rco1m to 921.6 KHz and the maximum baud rate of UART is limited to 115200.

The rco1m is not restricted to the UART use and the Host CPU can use this clock also.

### 3.4. The 32 KHz RC Oscillator

The 32 KHz RC oscillator (rco32k) is used for slow-clock timers, like RTC timer and slow-clock Timer 0 and 1. The rco32k is kept power-on in Sleep Mode but is powered off in Deep Sleep Mode by default. For those applications required RTC Timer running in Deep Sleep Mode, the control register, cfg\_ds\_rco32k\_off, shall be set to 0b.

# 3.5. The 32 KHz Crystal Oscillator

CZ20 also supports the optional 32 KHz crystal oscillator (xo32k) that can replace the rco32k if a high-accuracy slow clock is needed.

Because the xo32k requires external pins to connect to the crystal, the support of xo32k is only available in certain types of packages.

### 3.6. Internal Clocks

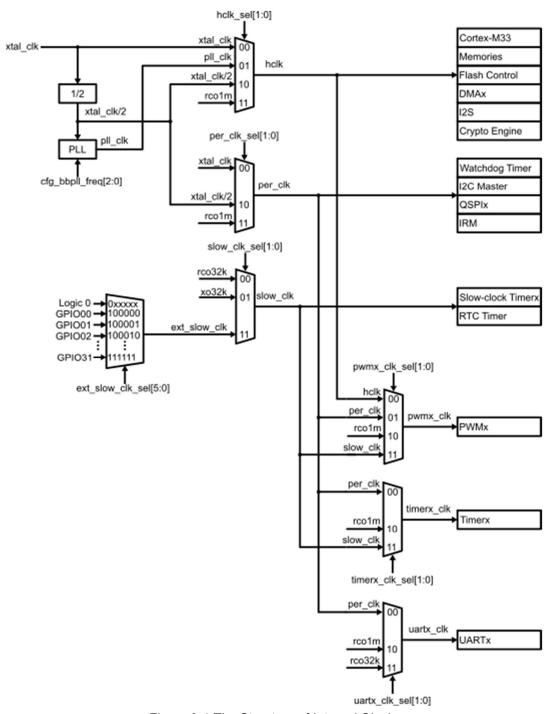

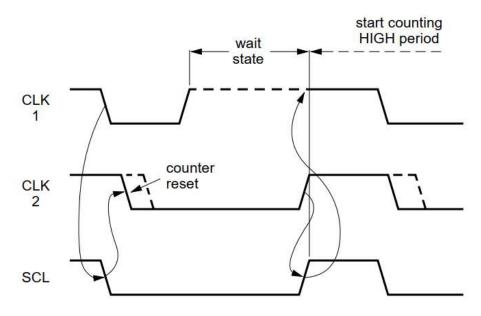

There are three major internal clocks that can be selected from above clock sources and they are hclk, per\_clk and slow\_clk. Some peripherals have their dedicated clocks derived from them. Table 3-3 summarizes those internal clocks and their usages. The structure of internal clocks is illustrated in Figure 3-1.

Table 3-3 Summary of Internal Clocks

| Internal Clock | Description       | Usage             |  |

|----------------|-------------------|-------------------|--|

| hclk           | AHB clock         | Host CPU          |  |

|                |                   | AHB/APB bus       |  |

|                |                   | Memories          |  |

|                |                   | DMAx              |  |

|                |                   | Flash             |  |

|                |                   | I2S               |  |

|                |                   | Crypto Engine     |  |

| slow_clk       | Slow clock        | RTC Timer         |  |

|                |                   | Slow-clock Timers |  |

| per_clk        | Peripheral clock  | Watchdog Timer    |  |

|                |                   | I2C Master        |  |

|                |                   | QSPIx             |  |

|                |                   | IRM               |  |

| pwmx_clk       | PWM clocks, where | PWMx              |  |

|                | x=0,1,2,3,4.      |                   |  |

| timerx_clk     | Timer clocks,     | Timerx            |  |

|                | where x=0,1,2.    |                   |  |

| uartx_clk      | UART clocks,      | UARTx             |  |

|                | where x=0,1,2.    |                   |  |

Although hclk and per\_clk can be selected independently, some combinations are undesired. It is very important that the frequency of hclk must be always great or equal than that of per\_clk.

Figure 3-1 The Structure of Internal Clocks

### 3.6.1. Selections of hclk

The hclk is used for those that require performance, such like the Host CPU, the bus system, the memories, and etc. The selection of hclk is controlled by the register, hclk\_sel, which is listed in Table 3-4.

Table 3-4 Selections of hclk

| hclk_sel[1:0] | hclk source |  |

|---------------|-------------|--|

| 00b           | xtal_clk    |  |

| 01b           | pll_clk     |  |

| 10b           | xtal_clk/2  |  |

| 11b           | rco1m       |  |

### 3.6.2. Selections of slow\_clk

The slow clock is used for slow-clock timers that is controlled by the register, slow\_clk\_sel, and is listed in Table 3-5.

Table 3-5 Selections of slow\_clk

| slow_clk_sel[1:0] | slow_clk source                 |  |

|-------------------|---------------------------------|--|

| 00b               | rco32k                          |  |

| 01b               | xo32k                           |  |

| 10b               | Reserved                        |  |

| 11b               | External slow clock (from GPIO) |  |

Besides the rco32k and xo32k, the slow\_clk can be come from the external clock source through the GPIO input. The register, ext\_slow\_clk\_sel, controls which GPIO is used that is summarized in Table 3-6.

Table 3-6 Select the GPIO for External Slow Clock

| Register              | Descriptions                                                  |  |  |  |  |

|-----------------------|---------------------------------------------------------------|--|--|--|--|

| ext_slow_clk_sel[5]   | External slow clock input enable.                             |  |  |  |  |

|                       | 0b Disable                                                    |  |  |  |  |

|                       | 1b Enable                                                     |  |  |  |  |

| ext_slow_clk_sel[4:0] | Select which GPIOxx is used as the external slow clock input. |  |  |  |  |

|                       | The value of 0x00 selects GPIO00 , the value 0x01 selects     |  |  |  |  |

|                       | GPIO01 and so on.                                             |  |  |  |  |

### 3.6.3. Selections of per\_clk

The per\_clk is used for Watchdog Timer, Timer 0/1/2, I2C Master 0/1, QSPI 0/1 and IRM. The control register, per\_clk\_sel, selects the clock source of per\_clk that is summarized in Table 3-7.

Table 3-7 Selections of per\_clk

| per_clk_sel[1:0] | per_clk source |

|------------------|----------------|

| 00b              | xtal_clk       |

| 01b              | Reserved       |

| 10b              | xtal_clk/2     |

| 11b              | rco1m          |

### 3.6.4. Selections of pwmx\_clk

There are five PWM modules and each of them has the dedicated clock selection. The control register, pwmx\_clk\_sel, selects the clock of the PWMx module.

Table 3-8 Selections of pwmx\_clk\_sel

| pwmx_clk_sel[1:0] | pwmx_clk source |

|-------------------|-----------------|

| 00b               | hclk            |

| 01b               | per_clk         |

| 10b               | rco1m           |

| 11b               | slow_clk        |

# 3.6.5. Selections of timerx\_clk

There are three Timer modules and each of them has the dedicated clock selection. The control register, timerx\_clk\_sel, selects the clock of the Timerx module.

Table 3-9 Selections of timerx\_clk\_sel

| timerx_clk_sel[1:0] | timerx_clk source |  |

|---------------------|-------------------|--|

| 00b                 | per_clk           |  |

| 01b                 | Reserved          |  |

| 10b                 | rco1m             |  |

| 11b                 | slow_clk          |  |

## 3.6.6. Selections of uartx\_clk

There are three UART modules and each of them has the dedicated clock selection. The control register, uartx\_clk\_sel, selects the clock of the UARTx module.

Table 3-10 Selections of uartx\_clk\_sel

| uartx_clk_sel[1:0] | uartx_clk source |

|--------------------|------------------|

|--------------------|------------------|

| 00b | per_clk  |

|-----|----------|

| 01b | Reserved |

| 10b | rco1m    |

| 11b | rco32k   |

If the rco1m is selected for the UART clock, the frequency of rco1m shall be calibrated to 921.6 KHz and the maximum baud rate is limited to 115200. If the rco32k is selected for the UART clock, the frequency of rco32k shall be calibrated to 38.4 KHz and the maximum baud rate is limited to 9600.

Because either rco1m or rco32k is still alive in low-power modes, the UART can receive data correctly and wake up the Host CPU in low-power modes when these clocks are used.

# 3.7. Registers of Clock Control

The clock control registers are resident in the System Control space whose base address is 0x50000000 for the secure partition or 0x40000000 for the non-secure partition.

### Offset 0x04: SYS\_CLK\_CTRL0

| Signal         | Bits    | Default | R/W | Description                                                                                             |

|----------------|---------|---------|-----|---------------------------------------------------------------------------------------------------------|

| Reserved       | [31:16] |         |     |                                                                                                         |

| cfg_bbpll_en   | [15]    | 0b      | R/W | Baseband PLL enable. 0b disable 1b enable                                                               |

| reserved       | [14:11] |         |     |                                                                                                         |

| cfg_bbpll_freq | [10:8]  | 000b    | R/W | The frequency selection of Baseband PLL 000b 48 MHz 001b 64 MHz 110b 36 MHz 111b 40 MHz Others Reserved |

| slow_clk_sel   | [7:6]   | 00b     | R/W | The selection of slow_clk.  00b rco32k  01b xo32k  10b reserved  11b external clock source from GPIOs   |

| reserved       | [5:4]   |         |     |                                                                                                         |

| per_clk_sel    | [3:2]   | 00b     | R/W | The selection of per_clk.  00b                                                                          |

| hclk_sel       | [1:0]   | 00b     | R/W | The selection of hclk.                                                                                  |

|  | 00b | xtal_clk   |

|--|-----|------------|

|  | 01b | pll_clk    |

|  | 10b | xtal_clk/2 |

|  | 11b | rco1m      |

# Offset 0x08: SYS\_CLK\_CTRL1

| Signal           | Bits    | Default | R/W   | Description                             |

|------------------|---------|---------|-------|-----------------------------------------|

| timer2_clk_sel   | [31:30] | 00b     | R/W   | The clock selection of Timer 0.         |

|                  |         |         |       | 00b per_clk                             |

|                  |         |         |       | 01b reserved                            |

|                  |         |         |       | 10b rco1m                               |

|                  |         |         |       | 11b slow_clk                            |

| timer1_clk_sel   | [29:28] | 00b     | R/W   | The clock selection of Timer 1.         |

|                  |         |         |       | 00b per_clk                             |

|                  |         |         |       | 01b reserved                            |

|                  |         |         |       | 10b rco1m                               |

|                  |         |         |       | 11b slow_clk                            |

| timer0_clk_sel   | [27:26] | 00b     | R/W   | The clock selection of Timer 0          |

|                  |         |         |       | 00b per_clk                             |

|                  |         |         |       | 01b reserved                            |

|                  |         |         |       | 10b rco1m                               |

|                  |         |         |       | 11b slow_clk                            |

| pwm4_clk_sel     | [25:24] | 00b     | R/W   | The clock selection of PWM4             |

|                  |         |         |       | 00b hclk                                |

|                  |         |         |       | 01b per_clk                             |

|                  |         |         |       | 10b rco1m                               |

|                  |         |         |       | 11b slow_clk                            |

| pwm3_clk_sel     | [23:22] | 00b     | R/W   | The clock selection of PWM3             |

|                  |         |         |       | 00b hclk                                |

|                  |         |         |       | 01b per_clk                             |

|                  |         |         |       | 10b rco1m                               |

|                  |         |         |       | 11b slow_clk                            |

| pwm2_clk_sel     | [21:20] | 00b     | R/W   | The clock selection of PWM2             |

|                  |         |         |       | 00b hclk                                |

|                  |         |         |       | 01b per_clk                             |

|                  |         |         |       | 10b rco1m                               |

| manual alla ant  | [40 40] | 001-    | D/\^/ | 11b slow_clk                            |

| pwm1_clk_sel     | [19:18] | 00b     | R/W   | The clock selection of PWM1             |

|                  |         |         |       | 00b hclk                                |

|                  |         |         |       | 01b per_clk                             |

|                  |         |         |       | 10b rco1m                               |

| muma0 alle sal   | [47:40] | 006     | D/\^/ | 11b slow_clk                            |

| pwm0_clk_sel     | [17:16] | 00b     | R/W   | The clock selection of PWM0             |

|                  |         |         |       | 00b hclk                                |

|                  |         |         |       | 01b per_clk                             |

|                  |         |         |       | 10b rco1m                               |

| rocomicad        | [15:14] |         | -     | 11b slow_clk                            |

| reserved         |         | 0,00    | D/\\/ | [12]: External alow alook input analys  |

| ext_slow_clk_sel | [13:8]  | 0x00    | R/W   | [13]: External slow clock input enable. |

|                  |         |         |       | 0b Disable                              |

|               |       |     |     | 1b Enable                                                |

|---------------|-------|-----|-----|----------------------------------------------------------|

|               |       |     |     | [12:8]: Select which GPIOxx is used as the external slow |

|               |       |     |     | clock input. The value of 0x00 selects GPIO00, the value |

|               |       |     |     | 0x01 selects GPIO01 and so on.                           |

| reserved      | [7:6] |     |     |                                                          |

| uart2_clk_sel | [5:4] | 00b | R/W | The clock selection of UART2                             |

|               |       |     |     | 00b per_clk                                              |

|               |       |     |     | 01b reserved                                             |

|               |       |     |     | 10b rco1m                                                |

|               |       |     |     | 11b rco32k                                               |

| uart1_clk_sel | [3:2] | 00b | R/W | The clock selection of UART1                             |

|               |       |     |     | 00b per_clk                                              |

|               |       |     |     | 01b reserved                                             |

|               |       |     |     | 10b rco1m                                                |

|               |       |     |     | 11b rco32k                                               |

| uart0_clk_sel | [1:0] | 00b | R/W | The clock selection of UART0                             |

|               |       |     |     | 00b per_clk                                              |

|               |       |     |     | 01b reserved                                             |

|               |       |     |     | 10b rco1m                                                |

|               |       |     |     | 11b rco32k                                               |

### 4. Resets

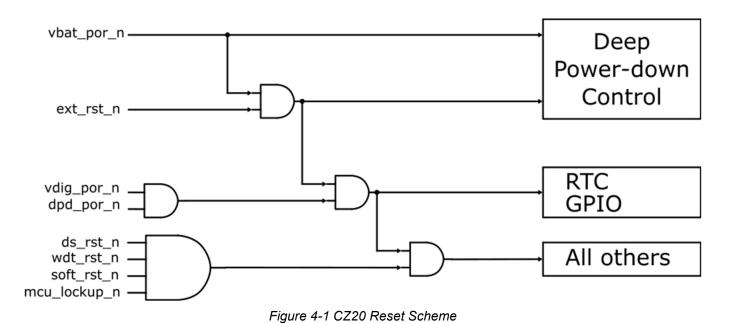

The reset sources and their targets of CZ20 is summarized in Table 4-1 and graphically illustrated in Figure 4-1.

| Reset Source                 | Туре           | Signal       |                               | Targets     |            |

|------------------------------|----------------|--------------|-------------------------------|-------------|------------|

|                              |                |              | Deep<br>Power-down<br>Control | RTC<br>GPIO | All others |

| VBAT                         | Power          | vbat_por_n   | 0                             | 0           | 0          |

| RST_N                        | External pin   | ext_rst_n    | 0                             | 0           | 0          |

| VDD_DIG                      | Power          | vdig_por_n   |                               | 0           | 0          |

| Deep power-down wakeup reset | Internal event | dpd_rst_n    |                               | 0           | 0          |

| Deepsleep wakeup reset       | Internal event | ds_rst_n     |                               |             | 0          |

| Watchdog reset               | Internal event | wdt_rst_n    |                               |             | 0          |

| Software reset               | Internal event | soft_rst_n   |                               |             | 0          |

| MCU lockup                   | Internal event | mcu_lockup_n |                               |             | 0          |

Table 4-1 Reset Sources and Their Targets

T32CZ20 Reference Manual MAN-ZW-0002-02

#### 4.1. Power-on Reset

The power-on reset, vbat\_por\_n, is triggered when the power source, VBAT, is above the pre-defined threshold. It has the highest priority over other reset signals and will reset the whole system as illustrated in Figure 4-1.

#### 4.2. External Reset

There is a low-actively external reset pin, RST\_N, that can reset the whole chip externally. To active the external reset, RST\_N shall be asserted for at least 100us. A 100K ohm pull-up resistor is attached to the RST\_N pin internally so RST\_N can be left floating if not used.

# 4.3. Deep Power-down Wakeup Reset

During Deep Power-down mode, the whole chip is powered off except the Deep Power-down Control. After waking up from the Deep Power-down mode, the reset signal, dpd\_rst\_n, will be triggerd to reset the whole chip.

### 4.4. Deepsleep Wakeup Reset

During Deepsleep mode, most of the digital parts are powered off to reduce the leakage current. To let the digital circuits work correctly after waking up from Deepsleep, a Deepsleep wakeup reset signal, ds rst n, is generated automatically by the hardware to reset the corresponding digital circuits.

# 4.5. Watchdog Reset

When Watchdog Timer is not kicked for a certain period, the watchdog reset is triggered. Please refer to Chapter 15 Watchdog Timer for operations of Watchdog Timer in detail.

### 4.6. Software Reset

The software reset is triggered when the SYSRESETREQ bit in AIRCR register of Cortex-M33 is set. Please refer to the documents of Cortex-M33 for how to set SYSRESETREQ.

## 4.7. MCU Lockup

The Cortex-M33 enters a lockup state if a fault occurs when it cannot be serviced or escalated. In this situation, the processor does not execute any instructions and asserts the LOCKUP signal. It will then trigger the hardware controller to reset the entire the system.

# 4.8. Registers of Reset Causes

Because either reset will result in the reboot of the software, there are reset cause registers that can be used to identify what causes the reboot. The reset cause registers are resident in the Deep Powerdown Control space whose base address is 0x50005000 for the secure partition or 0x40005000 for the non-secure partition.

The reset cause registers are reset by the power-on reset only and software shall clear them manually by writing 1b to the register bit, clr\_rst\_cause. Those registers are described below.

#### Offset 0x00: DPD\_RST\_CAUSE

| Signal         | Bits   | Default | R/W      | Description                                             |

|----------------|--------|---------|----------|---------------------------------------------------------|

| Reserved       | [31:7] |         |          | ·                                                       |

| rst_cause_lock | [6]    | 0b      | R        | High indicates the reset cause is the mcu lockup.       |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_soft | [5]    | 0b      | R        | High indicates the reset cause is the software reset.   |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_wdt  | [4]    | 0b      | R        | High indicates the reset cause is the watchdog reset.   |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_ds   | [3]    |         |          | High indicates the reset cause is the Deepsleep wakeup. |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_dpd  | [2]    | 0b      | <u> </u> |                                                         |

|                |        |         |          | wakeup.                                                 |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_ext  | [1]    | 0b      | R        | High indicates the reset cause is the external reset.   |

|                |        |         |          | Cleared by clr_rst_cause.                               |

| rst_cause_por  | [0]    | 1b      | R        | High indicates the reset cause is the power-on reset.   |

|                |        |         |          | Cleared by clr_rst_cause.                               |

#### Offset 0x04: DPD\_CMD

| Signal        | Bits   | Default | R/W                | Description                            |

|---------------|--------|---------|--------------------|----------------------------------------|

| Reserved      | [31:1] |         |                    |                                        |

| clr_rst_cause | [0]    | 0b      | W1C <sup>(1)</sup> | Write 1 to clear all reset cause to 0. |

<sup>(1)</sup>W1C means "write 1 and auto clear".

### 5. Low Power Modes

Almost IoT devices are battery powered and some of them requires very long battery life. This makes the current consumption very critical. CZ20 has several low-power modes that will provide different degrees of power saving. Those low-power modes are WFI/WFE, Sleep, Deep Sleep and Deep Powerdown.

Low-power modes are triggered by WFI or WFE instruction of the CPU. In cooperated with the cfg\_set\_lowpower register in System Control, software can decide whether to enter those low-power modes or not. Software shall set cfg\_set\_lowpower correctly before executing WFI or WFE instruction. The cfg\_set\_lowpoor setting for each low-power mode is listed in below table.

cfg\_set\_lowpoer settings

Power Modes

000b

WFI / WFE only

001b

Sleep

01xb

Deep Sleep

1xxb

Deep Power-down

Table 5-1 Register Settings of Low-power Modes

Major characteristics of those low power states are summarized in Table 5-2. Because states of CPU are lost in Deep Sleep and Deep Power-down modes, CPU will be reboot when waking up from these two modes.

Table 5-2 Summary of Low-power Modes

| Power Modes     | Active LDOs                               | Active Clocks                                        | CPU State         | Memory          | Wakeup              |

|-----------------|-------------------------------------------|------------------------------------------------------|-------------------|-----------------|---------------------|

| Normal          | MV DCDC/(LDO)*<br>LV LDO<br>Retention LDO | RCO32K/(XO32K)<br>XO32M<br>(Baseband PLL)<br>(RCO1M) | Active<br>WFI/WFE | On              | Interrupts          |

| Sleep           | Retention LDO                             | RCO32K/(XO32K)<br>(RCO1M)                            | WFI/WFE           | Retention       | Interrupts          |

| Deep Sleep      | Retention LDO                             | Off/(RCO32K/XO32K)                                   | Off               | Off/(Retention) | GPIO<br>(RTC timer) |

| Deep Power-down | None                                      | None                                                 | Off.              | Off             | GPIO                |

<sup>\*</sup>Items inside ( ) are optional.

## 5.1. Power Domains of Peripherals

In order to further reduce the leakage current in low-power modes, peripherals are partitioned into 4 power domains according to their functionalities in Sleep and Deepsleep modes. Table 5-3 shows the default behaviors of each peripheral power domain in each low-power mode.

Table 5-3 Power Domains of Peripherals

| Power Domain  | Peripherals                                                                            | Sleep | Deepsleep | Deep Power-down |

|---------------|----------------------------------------------------------------------------------------|-------|-----------|-----------------|

| Always on     | RTC Timer GPIO Control Watchdog Timer AUX Comparator BOD Comparator RCO32K Calibration | On    | On        | Off             |

| Peripherals 1 | Cortex-M33 Flash Control UART 0 I2C Slave Slow-clock Timer 0/1 Security Control        | On    | Off       | Off             |

| Peripherals 2 | PWM DMA 0/1 UART 2 QSPI 0/1 Crypto Engine I2C Master 0 I2C Master 1 AUX ADC IRM PUFrt  | Off   | Off       | Off             |

| Peripherals 3 | Cache Control UART 1 Timer 0/1/2 RCO1M Calibration FPU of Cortex-M33 DBG of Cortex-M33 | Off   | Off       | Off             |

Be aware of peripherals in Peripherals 2 Power domain. Because those peripherals are powered off in Sleep mode by default, their internal states are reset to the default values after waking up from Sleep mode. It is suggested to run initialization procedures of the peripheral every time when it is used.

## 5.2. Power Modes of COMM Subsys

Like the Host CPU, the COMM Subsys has its own power states and they are WFI/WFE only, Sleep and Deepsleep modes. The WEI/WFE only and Sleep mode are controlled by the COMM Subsys firmware regardless of the power states of Host CPU. Its Deepsleep mode is controlled by the Host CPU to power off entirely the COMM Subsys. Host CPU shall also power off the COMM Subsys if it wants to enter Deepsleep mode to minimize the current consumption.

Be aware to reload the firmware of COMM Subsys when wakes COMM Subsys from the Deepsleep since all status of COMM Subsys are lost in its Deepsleep mode. The Host CPU can do those operations through the COMM Subsys interface described in Chapter 7 COMM Subsys.

Because low-power modes of COMM Subsys also attempts to power down LDOs and Clocks of the system, the actual on/off states of LDOs and Clocks are determined by both Host CPU and COMM subsys. LDOs and Clocks of the system will be kept on if either Host CPU or COMM Subsys is in Normal mode.

## 5.3. Wakeup in Sleep Mode

Though all interrupts can wake up the system in Sleep Mode, however, only certain peripherals have the capability to generate interrupts in Sleep Mode. GPIOs, slow-clock Timers, RTC Timer, I2C Slave, AUX Comparators, BOD Comparator, UARTs, and COMM Subsys are such peripherals. Wakeup sources in Sleep Mode are summarized in Table 5-4.

| Wakeup Sources    | Conditions          | Comments                                                                                                                                                                                                             |  |  |

|-------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIOs             | No                  | N/A                                                                                                                                                                                                                  |  |  |

| Slow-clock Timers | No                  | N/A                                                                                                                                                                                                                  |  |  |

| RTC Timer         | No                  | N/A                                                                                                                                                                                                                  |  |  |

| I2C Slave         | No                  | N/A                                                                                                                                                                                                                  |  |  |

| AUX Comparator    | No                  | AUX Comparator shall be enabled in Sleep Mode.                                                                                                                                                                       |  |  |

| BOD Comparator    | No                  | BOD Comparator shall be enabled in Sleep Mode.                                                                                                                                                                       |  |  |

| UARTx             | uartx_clk_sel = 00b | uart_sleep_wake_en shall be set to 1b.     Only RX Break up to 1.5ms can wake up.                                                                                                                                    |  |  |

|                   | uartx_clk_sel = 10b | <ol> <li>uart_sleep_wake_en shall be set to 1b.</li> <li>The rco1m shall be enabled and calibrated to 921.6 KHz.</li> <li>UART can receive data and wake up in Sleep Mode with the baudrate up to 115200.</li> </ol> |  |  |

Table 5-4 Wakeup Sources in Sleep Mode

|             | uartx_clk_sel = 11b | <ol> <li>uart_sleep_wake_en shall be set to 1b.</li> <li>The rco32k shall be calibrated to 38.4 KHz.</li> <li>UART can receive data and wake up in Sleep Mode with the baudrate up to 9600.</li> </ol> |

|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMM Subsys | No                  | Controlled by the firmware of COMM Subsys                                                                                                                                                              |

# 5.4. Wakeup in Deep Sleep Mode

Wakeup sources in Deep Sleep Mode can be GPIOs, RTC Timer, AUX comparator and BOD comparator. Their settings are summarized below.

Table 5-5 Wakeup Sources in Deep Sleep Mode

| wakeup Sources | Comments                                                                                                                                                                                      |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIOx          | <ol> <li>The corresponding set_ds_wakeup_en[x] shall be set.</li> <li>Either set_ds_wakeup_high[x] or set_ds_wakeup_low[x] shall be set to determine the wakeup polarity of GPIOx.</li> </ol> |  |  |

| RTC Timer      | Either rco32k or xo32k shall be enabled in Deep Sleep Mode.                                                                                                                                   |  |  |

| AUX Comparator | AUX Comparator shall be enabled in Deep Sleep Mode.                                                                                                                                           |  |  |

| BOD Comparator | BOD Comparator shall be enabled in Deep Sleep Mode.                                                                                                                                           |  |  |

#### Wakeup in Deep Power-down Mode 5.5.

The Deep Power-down mode is the lowest power mode of CZ20. All internal clock sources and LDOs are powered off in this mode. All available GPIOs can be configured as the wakeup source by setting the registers, dpd gpio wake en and dpd gpio wake pol, in the memory space of Deep Power-down Control. Besides, there are 16-byte retention registers, also located in Deep Power-down Control, that can be used by Software. Data of those retention registers won't be lost until updating by Software or power-on reset.

#### Offset 0x08: DPD GPIO EN

| Signal           | Bits   | Default | R/W | Description                                                  |

|------------------|--------|---------|-----|--------------------------------------------------------------|

| dpd_gpio_wake_en | [31:0] | 0x0     | RW  | Set the corresponding GPIO as the wakeup source in Deep      |

|                  |        |         |     | Power-down Mode. For example, bit [0] is for GPIO00, bit [1] |

| is for GPIO01 and so on. |

|--------------------------|

| 0b disable               |

| 1b enable                |

### Offset 0x0C: DPD\_GPIO\_POL

| Signal            | Bits   | Default | R/W | Description                                                  |

|-------------------|--------|---------|-----|--------------------------------------------------------------|

| dpd_gpio_wake_pol | [31:0] | 0x0     | RW  | Set the wakeup polarity of the corresponding GPIO in Deep    |

|                   |        |         |     | Power-down Mode. For example, bit [0] is for GPIO00, bit [1] |

|                   |        |         |     | is for GPIO01 and so on.                                     |

|                   |        |         |     | 0b level low                                                 |

|                   |        |         |     | 1b level high                                                |

#### Offset 0x10: DPD\_RET0

| Signal          | Bits   | Default | R/W | Description           |  |

|-----------------|--------|---------|-----|-----------------------|--|

| dpd_retention_0 | [31:0] | 0x0     | RW  | Retention register 0. |  |

### Offset 0x14: DPD\_RET1

| Signal          | Bits   | Default | R/W | Description           |

|-----------------|--------|---------|-----|-----------------------|

| dpd_retention_1 | [31:0] | 0x0     | RW  | Retention register 1. |

#### Offset 0x18: DPD\_RET2

| Signal          | Bits   | Default | R/W | Description           |

|-----------------|--------|---------|-----|-----------------------|

| dpd_retention_2 | [31:0] | 0x0     | RW  | Retention register 2. |

#### Offset 0x1C: DPD RET3

| Signal          | Bits   | Default | R/W | Description           |

|-----------------|--------|---------|-----|-----------------------|

| dpd_retention_3 | [31:0] | 0x0     | RW  | Retention register 3. |

# 5.6. Memory Low-power Control

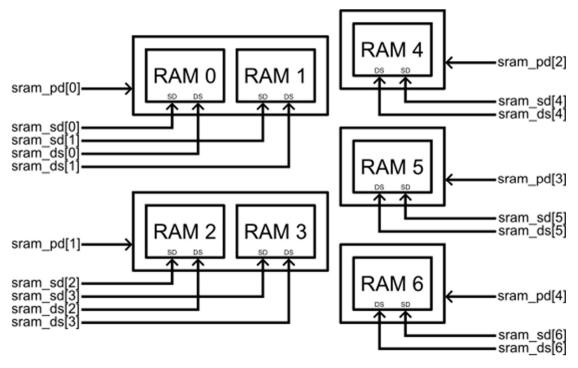

System memories are consisted of seven memory macros, RAM 0~6. Each memory macro has its own low-power modes, Deep sleep, Shutdown and Power down. When a memory macro is in Deep sleep mode, data is retained but memory access is not allowed. When a memory macro is in Shutdown or Power down mode, data will be lost. Power modes of memory macros are summarized in Table 5-6

Table 5-6 Power Modes of Memory Macros

| Power Mode | Controls                   | Memory Access | Data Retention |

|------------|----------------------------|---------------|----------------|

| Active     | sram_pd = 0<br>sram_sd = 0 | Allowed       | Yes            |

|           | sram_ds = 0 |             |     |

|-----------|-------------|-------------|-----|

|           | sram_pd = 0 |             |     |

| Deepsleep | sram_sd = 0 | Not allowed | Yes |

|           | sram_ds = 1 |             |     |

|           | sram_pd = 0 |             |     |

| Shutdown  | sram_sd = 1 | Not allowed | No  |

|           | sram_sd = x |             |     |

|           | sram_pd = 1 |             |     |

| Powerdown | sram_sd = x | Not allowed | No  |

|           | sram_sd = x |             |     |

To further reduce the current in system low-power modes, those memories are divided into several power domains and can be completely powered down as illustrated in Figure 5-1. Comparison of leakage current in those memory low-power modes is Powerdown < Shutdown < Deepsleep.

Figure 5-1 Power-domain Partition of Memories

Because RAM 0 and RAM 1 are in the same power domain, power off this power domain will power

down both RAM 0 and RAM 1 at the same time. If you want to retain data of either RAM 0 or RAM 1 is system low-power modes, you can't power off this power domain. Instead, you shall shut down the other. RAM 2 and RAM 3 are similar to RAM 0 and RAM 1 since they are also in one power domain.

RAM 4, RAM 5, and RAM 6 have their own power domain. It is suggested to use powerdown instead of shutdown if you won't to retain their data in system low-power modes.

Users can configure the power mode of individual memory macro in system low-power modes. Hardware will set memories in proper power modes according to the system power modes automatically.

Detailed registers for memory low-power control are resident in the System Control space whose base address is 0x50000000 for the secure partition or 0x40000000 for the non-secure partition. Those configuration registers have the same naming rule like cfg\_sram\_postfix1\_postfix2 while the postfix1 indicates the memory power mode and the postfix2 indicates the system power modes. For example, cfg\_sram\_ds\_sp is used to set the memory in Deepsleep mode when the system is in Sleep mode and cfg\_sram\_pd\_nm is used to set the memory in Powerdown mode when the system is in Normal mode.

#### Offset 0x50: SRAM\_LOWPOWER\_0

| Signal               | Bits    | <br>Default | R/W | Description                                                                                                                                                                                                                                                                                                      |

|----------------------|---------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_sram_ds_ds[15:0] | [31:16] | 0x0         | R/W | Set 1b to the individual bit to set SRAM in Deepsleep mode when System is in Deepsleep mode. cfg_sram_ds_ds [0] : RAM 0 cfg_sram_ds_ds [1] : RAM 1 cfg_sram_ds_ds [2] : RAM 2 cfg_sram_ds_ds [3] : RAM 3                                                                                                         |

|                      |         |             |     | cfg_sram_ds_ds [4] : RAM 4 cfg_sram_ds_ds [5] : RAM 5 cfg_sram_ds_ds [6] : RAM 6 Others : Reserved                                                                                                                                                                                                               |

| cfg_sram_ds_sp[15:0] | [15:0]  | 0x0         | R/W | Set 1b to the individual bit to set SRAM in  Deepsleep mode when System is in Sleep mode.  cfg_sram_ds_sp [0] : RAM 0  cfg_sram_ds_sp [1] : RAM 1  cfg_sram_ds_sp [2] : RAM 2  cfg_sram_ds_sp [3] : RAM 3  cfg_sram_ds_sp [4] : RAM 4  cfg_sram_ds_sp [5] : RAM 5  cfg_sram_ds_sp [6] : RAM 6  Others : Reserved |

#### Offset 0x54: SRAM LOWPOWER 1

| Signal               | Bits    | Default | R/W | Description                                 |

|----------------------|---------|---------|-----|---------------------------------------------|

| cfg_sram_sd_sp[15:0] | [31:16] | 0x0     | R/W | Set 1b to the individual bit to set SRAM in |

|                      |        |      |     | Shutdown mode when System is in Sleep mode.                                                                                                                                         |

|----------------------|--------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |        |      |     | cfg_sram_sd_sp [0] : RAM 0                                                                                                                                                          |

|                      |        |      |     | cfg_sram_sd_sp [1] : RAM 1                                                                                                                                                          |

|                      |        |      |     | cfg_sram_sd_sp [2] :RAM 2                                                                                                                                                           |

|                      |        |      |     | cfg_sram_sd_sp [3] :RAM 3                                                                                                                                                           |

|                      |        |      |     | cfg_sram_sd_sp [4] : RAM 4                                                                                                                                                          |

|                      |        |      |     | cfg_sram_sd_sp [5] : RAM 5                                                                                                                                                          |

|                      |        |      |     | cfg_sram_sd_sp [6] : RAM 6                                                                                                                                                          |

|                      |        |      |     | Others : Reserved                                                                                                                                                                   |

| cfg_sram_sd_nm[15:0] | [15:0] | 0x0  | R/W | Set 1b to the individual bit to set SRAM in                                                                                                                                         |

| 1 - 3                | []     | 0710 | ,   | Cot 15 to the marriagal sit to oct of will in                                                                                                                                       |

|                      | []     |      |     | Shutdown mode when System is in Normal mode.                                                                                                                                        |

|                      | []     |      |     |                                                                                                                                                                                     |

|                      | [10.0] |      |     | Shutdown mode when System is in Normal mode.                                                                                                                                        |

|                      | [10.0] |      |     | Shutdown mode when System is in Normal mode. cfg_sram_sd_nm [0] : RAM 0                                                                                                             |

|                      | [10.0] |      |     | Shutdown mode when System is in Normal mode. cfg_sram_sd_nm [0] : RAM 0 cfg_sram_sd_nm [1] : RAM 1                                                                                  |

|                      | [10.0] |      |     | Shutdown mode when System is in Normal mode. cfg_sram_sd_nm [0] : RAM 0 cfg_sram_sd_nm [1] : RAM 1 cfg_sram_sd_nm [2] : RAM 2                                                       |

|                      | [1000] |      |     | Shutdown mode when System is in Normal mode. cfg_sram_sd_nm [0] : RAM 0 cfg_sram_sd_nm [1] : RAM 1 cfg_sram_sd_nm [2] : RAM 2 cfg_sram_sd_nm [3] : RAM 3                            |

|                      | [100]  |      |     | Shutdown mode when System is in Normal mode. cfg_sram_sd_nm [0] : RAM 0 cfg_sram_sd_nm [1] : RAM 1 cfg_sram_sd_nm [2] : RAM 2 cfg_sram_sd_nm [3] : RAM 3 cfg_sram_sd_nm [4] : RAM 4 |

# Offset 0x58: SRAM\_LOWPOWER\_2

| Signal               | Bits    | Default | R/W | Description                                                                                                                                                                                                                                                                                     |

|----------------------|---------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_sram_pd_sp[7:0]  | [31:24] | 0x0     | R/W | Set 1b to the individual bit to set SRAM in Powerdown mode when System is in Sleep mode.  cfg_sram_pd_sp [0] : RAM 0 , RAM 1  cfg_sram_pd_sp [1] : RAM 2 , RAM 3  cfg_sram_pd_sp [2] : RAM 4  cfg_sram_pd_sp [3] : RAM 5  cfg_sram_pd_sp [4] : RAM 6  Others : Reserved                         |

| cfg_sram_pd_nm[7:0]  | [23:16] | 0x0     | R/W | Set 1b to the individual bit to set SRAM in Powerdown mode when System is in Normal mode.  cfg_sram_pd_nm [0] : RAM 0 , RAM 1  cfg_sram_pd_nm [1] : RAM 2 , RAM 3  cfg_sram_pd_nm [2] : RAM 4  cfg_sram_pd_nm [3] : RAM 5  cfg_sram_pd_nm [4] : RAM 6  Others : Reserved                        |

| cfg_sram_sd_ds[15:0] | [15:0]  | 0x0     | R/W | Set 1b to the individual bit to set SRAM in Shutdown mode when System is in Deepsleep mode.  cfg_sram_sd_ds [0] : RAM 0  cfg_sram_sd_ds [1] : RAM 1  cfg_sram_sd_ds [2] : RAM 2  cfg_sram_sd_ds [3] : RAM 3  cfg_sram_sd_ds [4] : RAM 4  cfg_sram_sd_ds [5] : RAM 5  cfg_sram_sd_ds [6] : RAM 6 |

|  |  | ï       |               |

|--|--|---------|---------------|

|  |  | ()there | · Reserved    |

|  |  | Othicis | . i tesei ved |

#### Offset 0x5C: SRAM LOWPOWER 3

| Signal              | Bits   | Default | R/W | Description                                                                                                                                                                                                                                                                 |

|---------------------|--------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reserved            | [31:8] |         |     |                                                                                                                                                                                                                                                                             |

| cfg_sram_pd_ds[7:0] | [7:0]  | 0x0     | R/W | Set 1b to the individual bit to set SRAM in Powerdown mode when System is in Deepsleep mode.  cfg_sram_pd_ds [0] : RAM 0 , RAM 1  cfg_sram_pd_ds [1] : RAM 2 , RAM 3  cfg_sram_pd_ds [2] : RAM 4  cfg_sram_pd_ds [3] : RAM 5  cfg_sram_pd_ds [4] : RAM 6  Others : Reserved |

# 5.7. Registers

Detailed registers for memory and peripheral low-power control are resident in the System Control space whose base address is 0x50000000 for the secure partition or 0x40000000 for the non-secure partition. Those configuration registers have the same naming rule like cfg\_sram\_postfix1\_postfix2 while the postfix1 indicates the memory power mode and the postfix2 indicates the system power modes. For example, cfg\_sram\_ds\_sp is used to set the memory in Deepsleep mode when the system is in Sleep mode and cfg\_sram\_pd\_nm is used to set the memory in Powerdown mode when the system is in Normal mode.

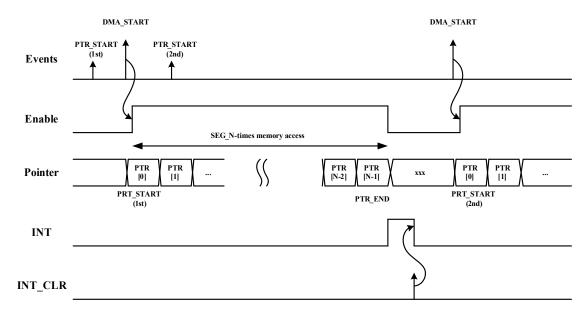

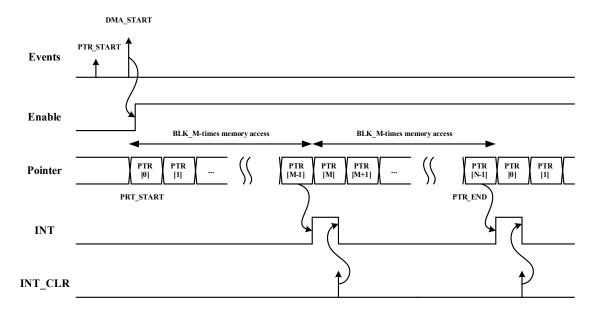

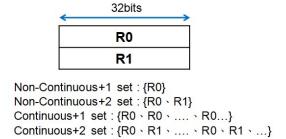

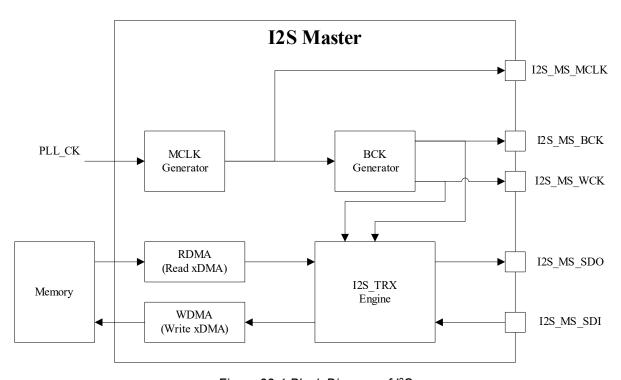

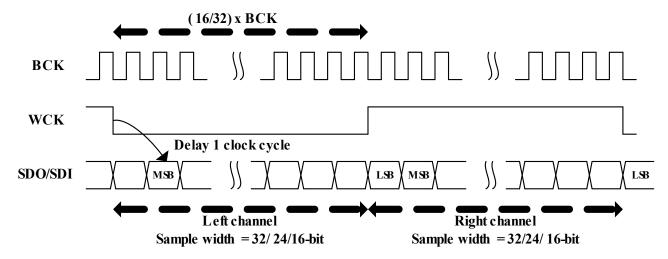

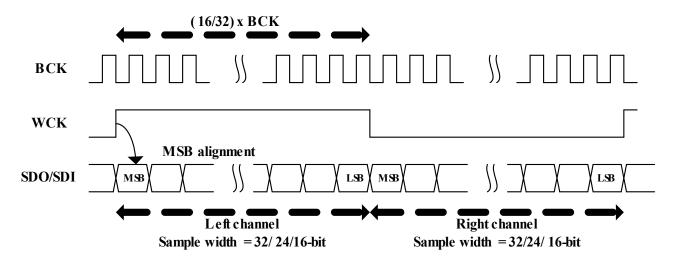

#### Offset 0x50: SRAM\_LOWPOWER\_0